Carry Skip Adder Circuit Diagram

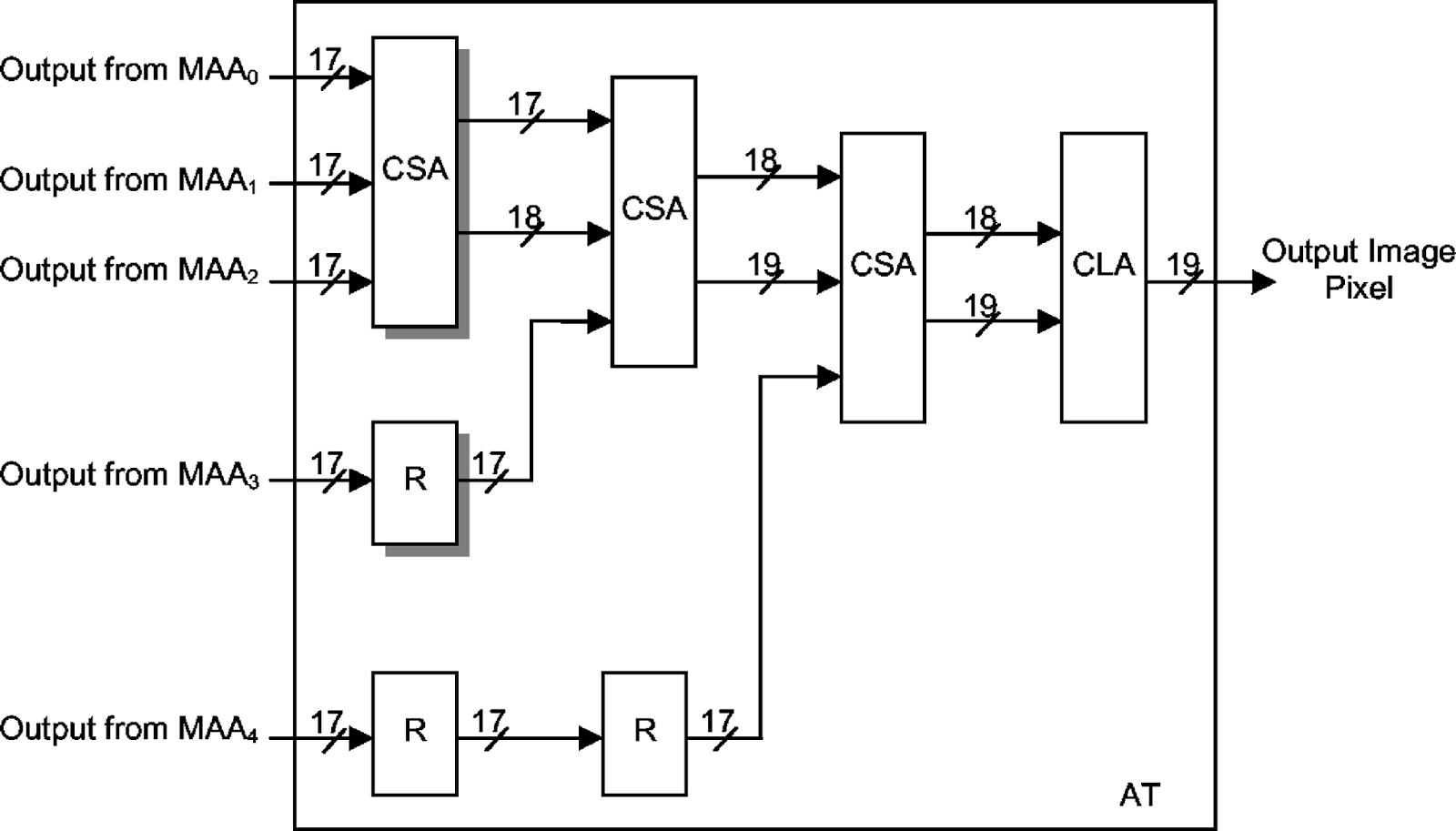

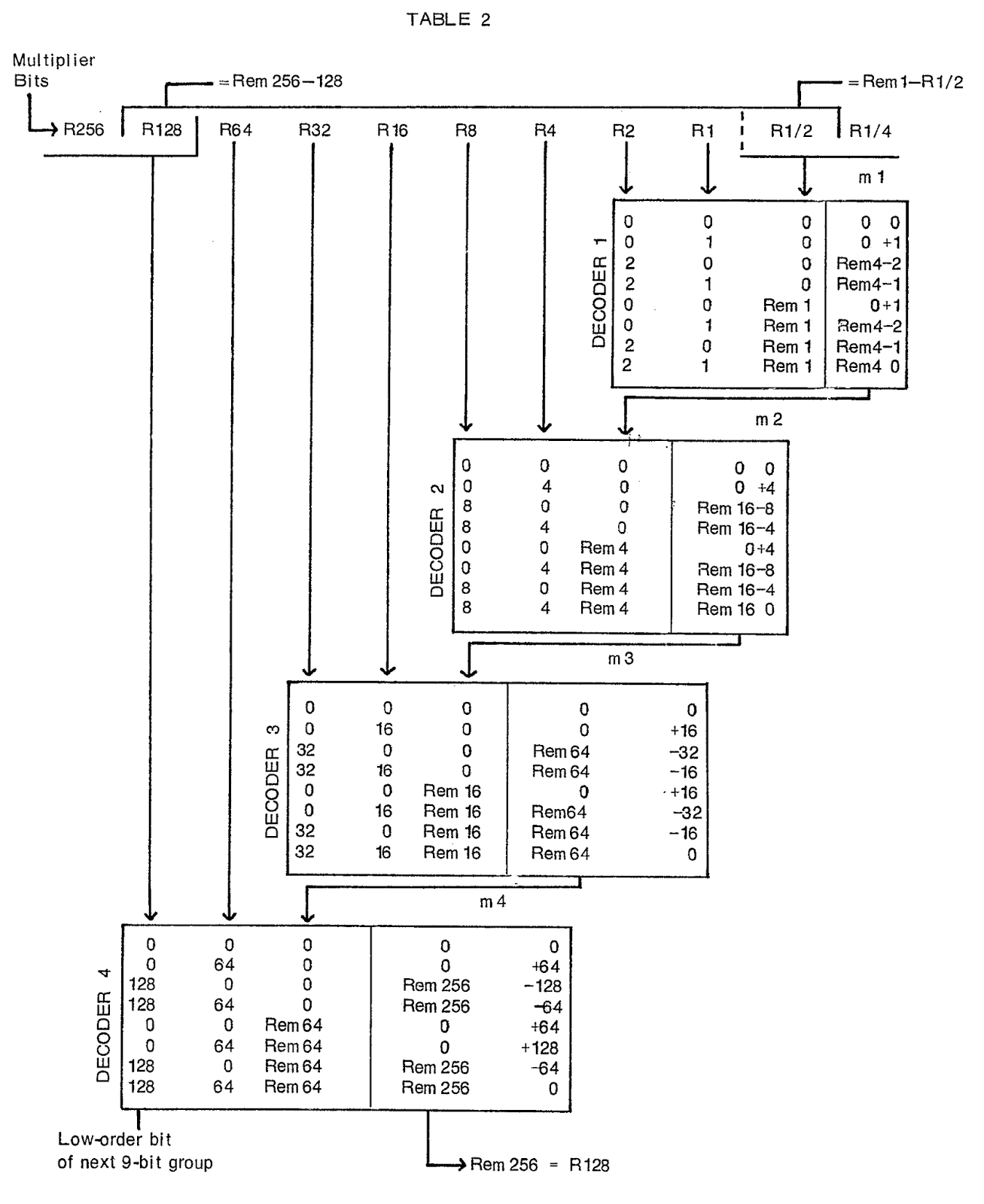

Carry adder ahead look logic digital ripple generator geeksforgeeks behave standard does source Adder carry topologies Adder carry save verilog architecture advantages multiplier bit tree ppt circuit diagram code

carry save adder - Scribd india

Schematic of carry skip adder Digital logic Adder carry

Adder ripple

Adder addersEee world, department of eee, adbu: ripple carry and carry look ahead adder Carry look ahead addersCarry save adder.

File:carry-select-adder-fixed-size.pngExplain carry skip adder Adder carry save multiplier bit binary circuit table diagram logic circuits advantages tree ppt truth verilog architecture codeBlock diagram of 4-bit ripple carry adder.

Carry save adder

Carry-skip adderCarry-skip adder Adder carry critical(pdf) area, delay and power comparison of adder topologies.

Carry adderAdder ripple eee .

Block diagram of 4-bit Ripple Carry Adder | Download Scientific Diagram

File:Carry-select-adder-fixed-size.png - Wikipedia

EEE World, Department of EEE, ADBU: Ripple Carry And Carry Look Ahead Adder

carry save adder - Scribd india

Carry-skip adder | Semantic Scholar

carry save adder - Scribd india

Explain Carry Skip Adder

digital logic - How does a "standard" ripple carry adder behave

Carry Look Ahead Adders - Computer Organization And Architecture - Teachics

(PDF) Area, Delay and Power Comparison of Adder Topologies